AMD Zen5 ‘Strix Point’ APU Cache Configuration Surfaces, 1MB of L2 Cache Per Each Zen5 Core & Zen5C Configuration Similar to Intel’s Strategy

Performancedatabases has leaked the cache configuration of AMD’s upcoming Zen5 based Strix Point APUs. Strix Point has already surfaced prior to this leak, read our previous article for more information. As per rumors, the cache structure shows a very close resemblance to Intel’s E-Core layout.

Zen5 ‘Strix Point’ Cache Design

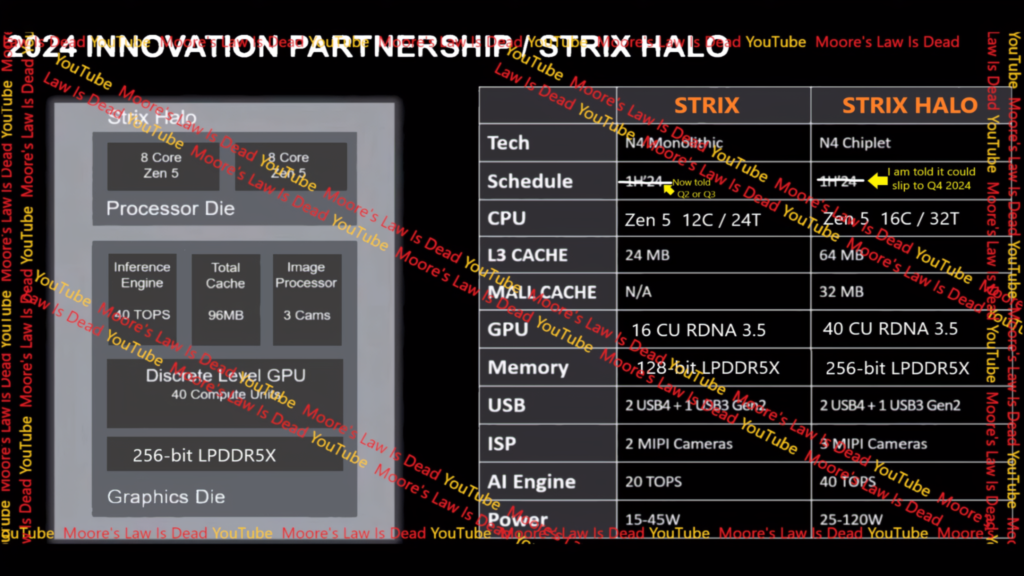

Strix Point will make use of both Zen5 and Zen5C cores. The highest configuration, at least for Strix Point Monolithic stands at 12 Cores / 24 Threads. This is the exact variant we’ll be covering in this article.

Strix Point will use a 4nm process node, and the top-of-the-line Ryzen 9 8040HS will have a TDP of 45W. The CPU packs 4x Zen5 Cores and 8x Zen5C cores, with SMT (Hyperthreading) enabled.

On both the P-Cores and E-Cores, the L1 Data Cache stands at 48kB with the L1 Instruction Cache at 32kB. Each Zen5 (P-Core) has 1MB of L2 Cache, for 4MB across the Zen5 cores.

The Zen5C or E-Cores are packed in groups of 4, similar to Intel’s efficient cores. Across each e-core cluster, we see 1MB of L2 Cache or 2MB for all 8 Zen5C cores. The total L3 cache amounts to 24MB as leaked previously by MLID.

The L2 Cache, at least across the Zen5C core cluster(s) does not seem much. This can seriously hamper the performance levels of these APUs. There are some mentions of a slight misreport by CPU-Z, though we are not certain.

Release Date

Strix Point APUs will come in two flavors, Strix Point Monolithic and Strix Point MCM (Strix Halo). Strix Halo should offer 16 Cores / 32 Threads and a 40 CU iGPU based on RDNA 3.5. These APUs will directly succeed the current-gen Phoenix Point offerings.

Strix Point is slated to arrive sometime in Q2 or Q3 2024, with Strix Halo planned for Q4 2024.

Source: Performancedatabases