Intel Also Prepping 3D Cache Technology for CPUs, Similar to AMD

Yesterday at the Innovation Event, Pat Gelsinger went live on stage and revealed many intriguing future Intel products. Meteor Lake, as expected, was in the spotlight alongside future Xeons and process technologies. Read our in-depth Meteor Lake architectural overview here.

Tom’s Hardware had a small Q/A Session with Pat Gelsinger at the Innovation Event. During the conversation, Intel effectively confirmed that it plans to develop 3D Cache Stacking tech somewhere in the future. This can not only be leveraged by Intel’s own CPUs but also by third-party fabless chip-makers if they choose to use Intel silicon.

Intel’s 3D Cache Stacking Tech to Rival AMD & TSMC

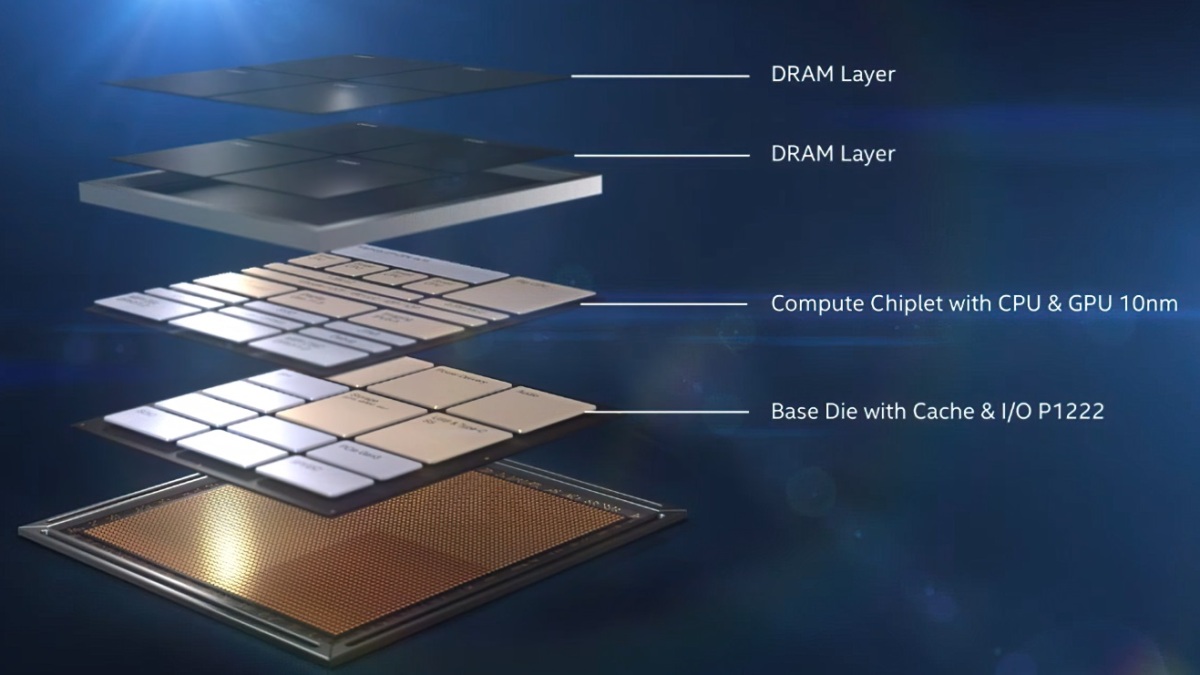

With Meteor Lake, Intel has stepped forth into the realm of 3D Packaging. Intel likes to call their approach ‘Foveros‘, and their chiplets ‘Tiles‘. Keeping this in mind, Tom’s Hardware directly asked Pat if Intel had any plans for a 3D V-Cache-like design.

It is very interesting that Pat was upfront regarding this and remarked that Intel does have future products that may integrate 3D Stacked Cache. Here is Pat’s response:

“When you reference V-Cache, you’re talking about a very specific technology that TSMC does with some of its customers as well. Obviously, we’re doing that differently in our composition, right? And that particular type of technology isn’t something that’s part of Meteor Lake, but in our roadmap, you’re seeing the idea of 3D silicon where we’ll have cache on one die, and we’ll have CPU compute on the stacked die on top of it, and obviously using EMIB that Foveros we’ll be able to compose different capabilities.”

Pat Gelsinger

The statement indicates that Intel will not just stack the cache tile over its Compute Tiles like AMD. Rather, Intel aims to put cache-equipped tiles on top of a possible base-tile and stack Compute Tiles on top. If we interpret this a bit further, Intel might stack multiple cache tiles with multiple Compute Tiles.

3D Stacking for All IFS Customers

The concept of 3D Cache Stacking is not exclusive to AMD and is actually offered by TSMC’s SoIC packaging technology. Intel can also use the same 3D Cache design, provided their silicon packaging is versatile enough.

If a client requires as such, Intel can integrate 3D Cache technology into their chips. The CEO has expressed serious confidence in the company’s ability, both as a CPU maker and as a Foundry Service to employ 3D Tile Stacking.

“We feel very good that we have advanced capabilities for next-generation memory architectures, advantages for 3D stacking, for both little die, as well as for very big packages for AI and high-performance servers as well. So we have a full breadth of those technologies. We’ll be using those for our products, as well as presenting it to the Foundry (IFS) customers as well,”

Pat Gelsinger

Moreover, future Xeons can go cache-dense and compete against their respective AMD counterparts. It is very important to note that Pat explicitly states Intel has 3D-Cache products scheduled in their roadmap.

The inclusion of vertically stacked cache in AMD’s mainstream Ryzen lineup has led to insanely efficient CPUs. All X3D CPUs are not just fast (in certain workloads) but also very power conservative. Under proper conditions, V-Cache acts as AMD’s trump card because the 7800X3D can sometimes easily eclipse both flagship Intel Core and Ryzen CPUs.

Source: Tom’s Hardware