AMD Zen5 Leaked to Offer 15% More IPC, Designed Using TSMC 4nm and 3nm Nodes & Planned for Launch in H1 2024

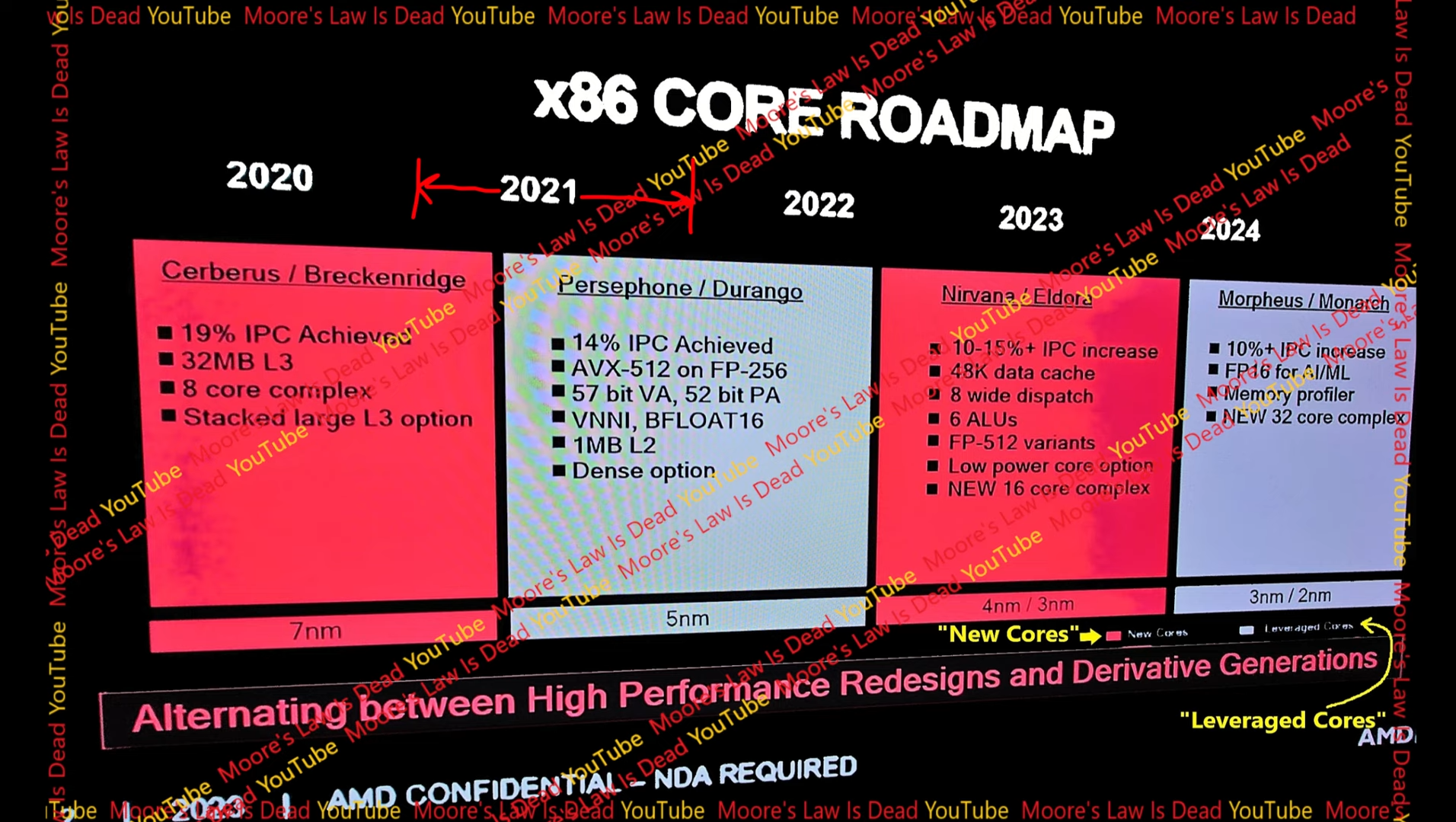

Moore’s Law Is Dead has leaked a lot of slides, schematics and information regarding AMD’s next-generation CPUs. The leak showcases a Zen5 ‘Nirvana‘ microarchitecture slide, expected performance, process nodes and the release date. Moreover, the leaker went forth and unveiled some very early Zen6 information as well.

Zen5 ‘Nirvana’ IPC Gains & Design

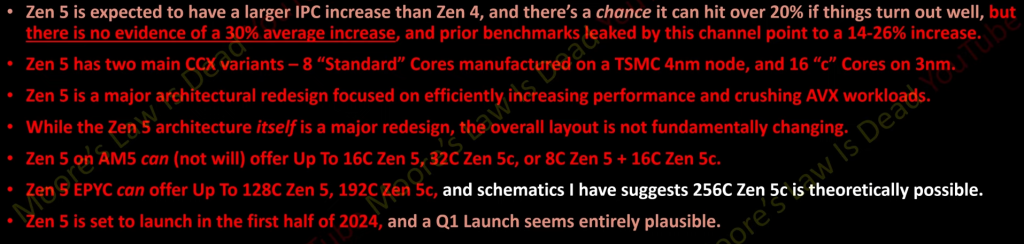

First off, MLID shared a microarchitecture schematic of Zen5. We will not delve into this, however, chip analyzers on Twitter are probably going to have a field day. MLID states that the new design overhaul should allow for better performance at lower clock speeds, which is beneficial for APUs.

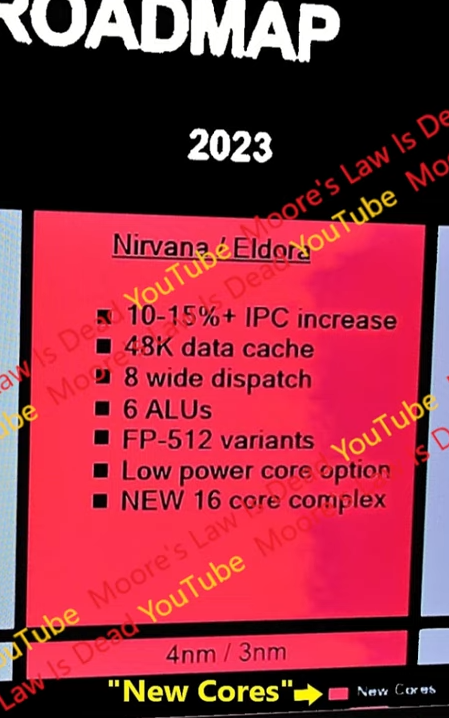

An old roadmap shows that AMD initially expected an IPC uplift of 10-15% from Zen4 to Zen5. We should remind users that AMD is rather conservative regarding their estimates, so the actual IPC uplift may be as high as 20%.

Interestingly, there is a ‘NEW 16 core complex‘ listing which should refer to Zen5c CCDs. It is very much possible that AMD could introduce efficient cores for mainstream desktop consumers.

IPC as a metric, is vague and is often an average of various benchmarks. Whatever IPC AMD mentions when Zen5 launches, through their extensive testing, should be in the ballpark of 10-15%, or even 20%. The Zen5 (P-Core) counterparts are rumored to utilize TSMC’s 4nm process, with Zen5c resorting to 3nm.

Theoretically, Zen5 can offer 8 Zen5 and 16 Zen5C (24 Cores), but that’s not confirmed by any means. As for Turin, complying with a previous rumor, the highest-end offering will go up to 128 Zen5 Cores. Similarly, Turin-Dense (Bergamo-Next) will pack 192 Zen5C cores, though 256 Zen5C cores is a possibility as well.

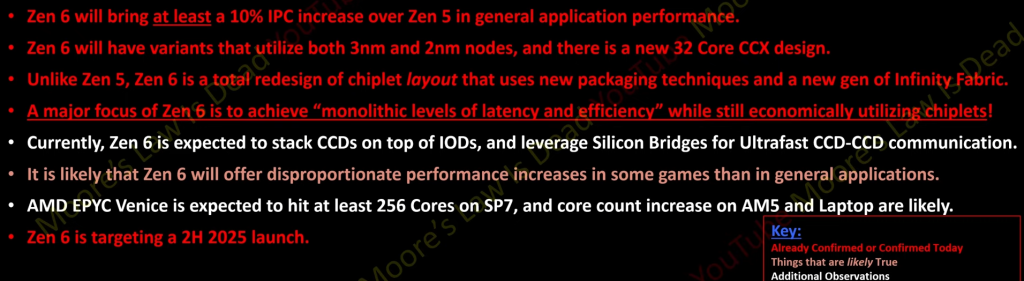

Zen6 ‘Morpheus’, The Biggest Architectural Leap Since Zen2

With Zen2, AMD opted for a significant paradigm transition with the new MCM layout. This was technically an industry-first, allowing AMD to leapfrog Intel with the next iteration, Zen3. Zen6 is no different as it is expected to stack CCDs on top of IODs, for a true 3D Chiplet Design.

Zen6, is at minimum 10% faster in terms of IPC than Zen5. Moreover, it is expected to leverage the 3nm and 2nm processes, which at the time will be bleeding-edge. Zen6 will compete against Panther Lake, which launches in 2025 and uses the 18A node (1.8nm equivalent).

Due to the 3D design, there might be discrepancies in Zen6’s performance uplifts, depending on the workload. Based on Zen6, EPYC Venice will go as high as 256 Zen6 Cores (SP7 Socket) with core counts possibly increased for desktop/laptop. AMD expects Zen6 to hit shelves by the second half of 2025.

Source: MLID